## IBM System Blue Gene Solution Blue Gene/Q Application Development

# Redbooks

ibm.com/redbooks

International Technical Support Organization

#### IBM System Blue Gene Solution: Blue Gene/Q Application Development

June 2013

**Note:** Before using this information and the product it supports, read the information in "Notices" on page vii.

#### Second Edition (June 2013)

This edition applies to Version 1, Release 1, Modification 2 of IBM Blue Gene/Q (product number 5733-BGQ).

#### © Copyright International Business Machines Corporation 2012, 2013. All rights reserved.

Note to U.S. Government Users Restricted Rights -- Use, duplication or disclosure restricted by GSA ADP Schedule Contract with IBM Corp.

### Contents

| Notices                                            | vii    |

|----------------------------------------------------|--------|

| Trademarks                                         | ix     |

| Preface                                            |        |

| Author                                             |        |

| Now you can become a published author, too!        | xii    |

| Comments welcome                                   |        |

| Stay connected to IBM Redbooks                     | . xiii |

| Summary of changes                                 |        |

| June 2013, Second Edition                          | XV     |

| Chapter 1. System overview                         | 1      |

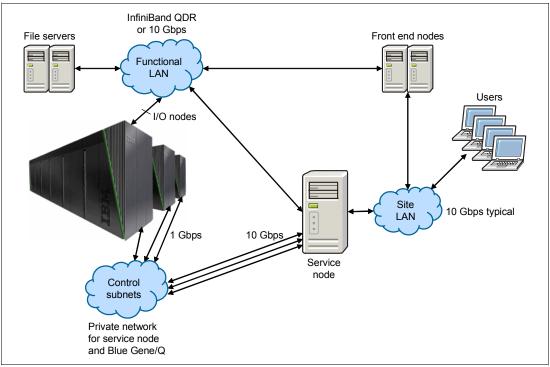

| 1.1 Blue Gene/Q environment overview               | 2      |

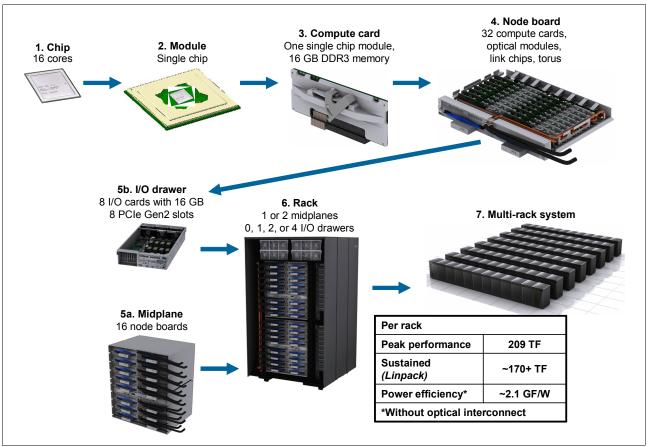

| 1.2 Blue Gene/Q hardware overview                  |        |

| 1.3 Blue Gene/Q software overview                  | 4      |

| 1.3.1 System administration and management         | 4      |

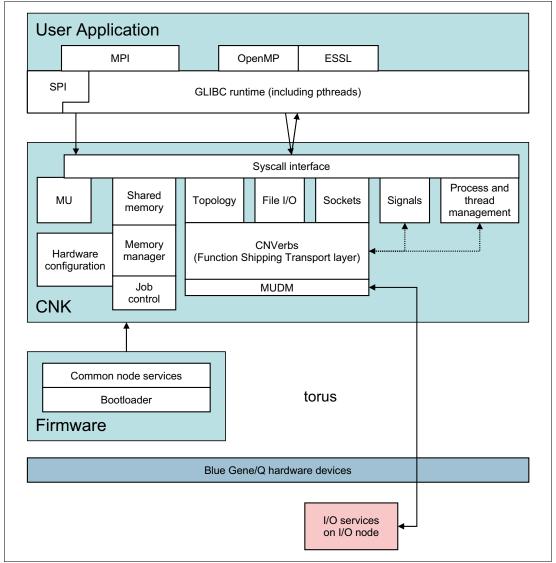

| 1.3.2 Compute Node Kernel and services             |        |

| 1.3.3 I/O node kernel and services                 |        |

| 1.3.4 Message Passing Interface                    |        |

| 1.3.5 Compilers                                    |        |

| 1.3.6 Application development and debugging        | 6      |

| Chapter 2 Kernel functionality                     | 9      |

| 2.1 Compute Node Kernel                            |        |

| 2.1.1 Stateless compute nodes                      |        |

| 2.1.2 Firmware                                     |        |

| 2.2 Role of the I/O node kernel                    | 12     |

| Chapter 3. Processes                               |        |

| 3.1 Importance of process count                    |        |

| 3.2 Process creation                               |        |

| 3.3 Processes per node                             |        |

| 3.4 Determining how many processes per node to use |        |

| 3.5 Specifying process count                       |        |

| 3.6 Support for 64-bit applications                |        |

| 3.7 Object identifiers                             |        |

| 3.7.1 Process identifier                           |        |

| 3.7.2 Thread identifier                            |        |

| 3.7.3 Thread group identifier                      |        |

| 3.7.4 T coordinate                                 |        |

| 3.8 Sub-node jobs                                  |        |

| 3.9 Threading overview                             |        |

| 3.9.1 Hardware thread over-commitment.             |        |

| 3.10 Thread scheduler                              |        |

| 3.10.1 Thread preemption                           |        |

| 3.10.2 Thread yield                                |        |

| 3.10.3 Round-robin dispatch                        |        |

| 3.11 Thread affinity                               | . 19   |

| 3.11.2 Depth-first assignment       19         3.11.4 Setting affinity with the pthread attribute       20         3.11.5 Setting affinity with the system call       20         3.11.5 Setting affinity with the system call       20         3.11.5 Setting affinity with the system call       20         3.12 Thread priority       21         3.12.1 Setting priority through the pthread attribute       22         3.12.2 Exploit setting of priority       23         S.12.3 Hardware thread priority       23         Chapter 4. Memory       25         4.1 Memory system overview       26         4.1.1 L 1 prefetch cache overview       26         4.1.2 L2 cache functional overview       28         4.1.3 Boot eDRAM overview       28         4.3 Memory protection       29         4.4 Shared memory       29         4.5 Persistent memory       29         4.6 Compute node ramdisk       30         4.7 Support for the /proc lile system       31         4.8 L1P prefetcher       32         4.8 L1 Prefetcher API descriptions       38         4.8 L1P prefetcher API descriptions       38         4.8 L1 Profetcher API descriptions       52         4.9 L2 taronic operations       52                                      | 3.11.1 Breadth-first assignment                                                                                                                                                          |                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 3.11.4 Setting affinity with the pythread attribute.       20         3.11.6 Extended thread affinity control       20         3.11.6 Extended thread affinity control       20         3.12.1 Setting priority through the phread attribute       22         3.12.1 Setting of priority       23         3.12.3 Hardware thread priority       23         3.12.4 Interact thread priority       23         3.12.5 Hardware thread priority       23         3.12.4 Hermory       25         4.1 Memory system overview       26         4.1.1 Liprefetch cache overview       26         4.1.2 L2 cache functional overview       28         4.1.3 Boot eDRAM overview       28         4.1.4 Shared memory       29         4.3 Bared memory       29         4.4 Shared memory       30         4.5 Persistent memory       30         4.6 Compute node ramdisk.       30         4.7 Support for the /proc file system       31         4.8 L1P prefetcher API descriptions       38         4.8.1 Directed prefetcher overview       34         4.8.2 Performan                                    |                                                                                                                                                                                          |                                  |

| 3.11.5 Setting affinity with the system call       20         3.12 Thread priority       20         3.12 Thread priority       20         3.12.1 Setting priority through the pthread attribute       22         3.12.2 Explicit setting of priority       23         3.12.3 Hardware thread priority       23         3.12.4 Hardware thread priority       23         3.12.5 Explicit setting of priority       23         3.12.1 It prefetch cache overview       26         4.1.1 Lip refetch cache overview       26         4.1.1 It prefetch cache overview       28         4.1.3 Boot eDRAM overview       28         4.1.3 Boot eDRAM overview       28         4.1.4 Boot eDRAM overview       29         4.5 Memory protection       29         4.6 Compute node ramdisk.       30         4.6 Compute node ramdisk.       30         4.7 Support for the /proc file system       31         4.8 LiP prefetcher       32         4.8.1 Prefetcher API descriptions       38         4.8.2 Perfect prefetcher overview       33         4.8.3 LiP prefetcher API descriptions       53         4.11 Speculative execution       53         4.12 transactional memory.       54         4.12 transactional me                                    | •                                                                                                                                                                                        |                                  |

| 3.11.6 Extended thread affinity control       20         3.12 Thread priority       21         3.12.1 Setting priority through the pthread attribute.       22         3.12.2 Explicit setting of priority.       23         3.12.3 Hardware thread priority       23         3.12.4 Kenton explicit setting of priority.       23         3.12.5 Hardware thread priority       23         3.12.3 Hardware thread priority       23         3.12.4 Kenton explicit setting of priority       23         3.12.5 Hardware thread priority       23         3.12.1 Hardware thread priority       23         3.12.2 Explicit setting of priority       23         3.12.3 Hardware thread priority       23         3.13 Boot eDRAM overview       26         4.1.1 L1 prefetch cache overview       28         4.1.2 L2 cache functional overview       28         4.1.3 Boot eDRAM overview       28         4.2 Memory protection       29         4.3 Stard memory       29         4.4 Shared memory       29         4.5 Persistent memory       30         4.6 Compute node randisk.       30         4.7 Support for the /proc file system       31         4.8 L1 Prefetcher.       32         4.8 L1 Prefetcher                                     | • • •                                                                                                                                                                                    |                                  |

| 3.12 Thread priority through the phread attribute       21         3.12.1 Setting priority through the phread attribute       22         3.12.2 Explicit setting of priority       23         3.12.3 Hardware thread priority       23         Chapter 4. Memory       25         4.1 Memory system overview       26         4.1.1 L1 prefetch cache overview       26         4.1.2 L2 cache functional overview       28         4.1.3 Boot eDRAM overview       28         4.3 Memory protection       29         4.4 Shared memory       29         4.5 Persistent memory       29         4.6 Compute node randisk.       30         4.6 Compute node randisk.       30         4.8 L1P prefetcher       32         4.8 L1P prefetcher       32         4.8.1 Linear stream prefetcher overview       33         4.8.2 Perfect prefetcher overview       33         4.8.3 L1P prefetcher API descriptions       38         4.8.4 Performance considerations       52         4.9 L2 atomic operations       53         4.10 Speculative execution       53         4.11 Support for dynamic linking       54         4.12 Transactional memory.       54         5.1 Lightweight principles       56 <td></td> <td></td>                             |                                                                                                                                                                                          |                                  |

| 3.12.1 Setting priority through the pthread attribute.       22         3.12.2 Explicit setting of priority       23         3.12.3 Hardware thread priority       23         Chapter 4. Memory       25         4.1 Memory system overview       26         4.1.1 L1 prefetch cache overview       26         4.1.3 Boot eDRAM overview       28         4.1.3 Boot eDRAM overview       28         4.1.4 Shore to the functional overview       28         4.2 Memory management.       29         4.3 Memory protection       29         4.4 Shared memory.       29         4.5 Persistent memory       30         4.6 Compute node ramdisk.       30         4.7 Support for the /proc file system       31         4.8 L1P prefetcher       32         4.8.1 Linear stream prefetcher overview       34         4.8.2 L1P prefetcher API descriptions       38         4.8.4 Perfort prefetcher overview       33         4.9 L2 atomic operations.       53         4.10 Speculative execution       53         4.11 Support for dynamic linking.       54         4.12 Transactional memory.       54         52 Kernel access       55         5.1 Lightweight principles       56                                                                |                                                                                                                                                                                          |                                  |

| 3.12.2       Explicit setting of priority.       23         3.12.3       Hardware thread priority       23         Chapter 4.       Memory       25         4.1       Memory system overview       26         4.1.1       L1 prefetch cache overview       26         4.1.2       L2 cache functional overview       28         4.1.3       Boot eDRAM overview       28         4.1.4       L2 cache functional overview       28         4.1.5       Memory management       29         4.4       Memory protection       29         4.5       Persistent memory       30         4.5       Persistent memory       30         4.6       Compute node ramdisk       30         4.7       Support for the /proc file system       31         4.8       L1P prefetcher overview       33         4.8.1       Linear stream prefetcher overview       34         4.8.1       Prefetcher aPI descriptions       38         4.8.4       Perfect prefetcher aVPI descriptions       38         4.8.4       Perfort prefetcher overview       53         4.10       Speculative execution       53         4.11       Support for dynamic linking       54                                                                                                      |                                                                                                                                                                                          |                                  |

| 3.12.3 Hardware thread priority       23         Chapter 4. Memory       25         4.1 Memory system overview       26         4.1.1 L1 prefetch cache overview       26         4.1.2 L2 cache functional overview       28         4.1.3 Boot eDRAM overview       28         4.1.3 Boot eDRAM overview       28         4.1.3 Boot eDRAM overview       28         4.1.4 Boot eDRAM overview       28         4.1.5 Boot eDRAM overview       28         4.1.6 Computer node ramdisk       29         4.5 Persistent memory       29         4.6 Compute node ramdisk       30         4.7 Support for the /proc file system       31         4.8 L1P prefetcher       32         4.8.1 Linear stream prefetcher overview       34         4.8.2 Perfect prefetcher overview       34         4.8.3 L1P prefetcher API descriptions       38         4.8.4 Performance considerations       53         4.10 Speculative execution       53         4.11 Support for dynamic linking.       54         12 Transactional memory.       54         Chapter 5. Compute Node Kernel interfaces       55         5.1 Lightweight principles       56         5.2.1 Application programming interface.       62 </td <td></td> <td></td>                      |                                                                                                                                                                                          |                                  |

| Chapter 4. Memory       25         4.1 Memory system overview       26         4.1.1 L1 prefetch cache overview       26         4.1.2 L2 cache functional overview       26         4.1.3 Boot eDRAM overview       28         4.1.3 Boot eDRAM overview       28         4.1.3 Boot eDRAM overview       28         4.2 Memory management.       29         4.3 Memory protection       29         4.4 Shared memory.       29         4.5 Persistent memory       30         4.6 Compute node ramdisk.       30         4.7 Support for the /proc file system       31         4.8 L1P prefetcher       32         4.8.1 Linear stream prefetcher overview       34         4.8.2 Perfect prefetcher overview       34         4.8.3 L1P prefetcher overview       34         4.8.4 Performance considerations       52         4.9 L2 atomic operations       53         4.10 Speculative execution       53         4.11 Explication programming interfaces       55         5.1 Lightweight principles       56         5.2.2 Application programming interfaces       56         5.2.3 System calls       63         Chapter 6. Parallel paradigms       65         6.1 Progr                                                                       |                                                                                                                                                                                          |                                  |

| 4.1 Memory system overview       26         4.1.1 L1 prefetch cache overview       26         4.1.2 L2 cache functional overview       28         4.1.3 Boot eDRAM overview       28         4.1.3 Boot eDRAM overview       28         4.1.3 Boot eDRAM overview       28         4.1.4 Boot eDRAM overview       28         4.1.5 Memory management       29         4.4 Shared memory       29         4.5 Persistent memory       29         4.5 Presistent memory       29         4.5 Compute node randisk       30         4.6 Compute node randisk       30         4.7 Support for the /prof file system       31         4.8 L1P prefetcher       32         4.8.1 Linear stream prefetcher overview       34         4.8.2 Perfect prefetcher overview       34         4.8.3 L1P prefetcher API descriptions       38         4.8.4 Performance considerations       52         4.9 L2 atomic operations       53         4.10 Speculative execution       53         4.11 Support for dynamic linking       54         4.12 Transactional memory       54         5.1 Lightweight principles       56         5.2 Kernel access       56         5.2.1 Application prog                                                                       |                                                                                                                                                                                          | 20                               |

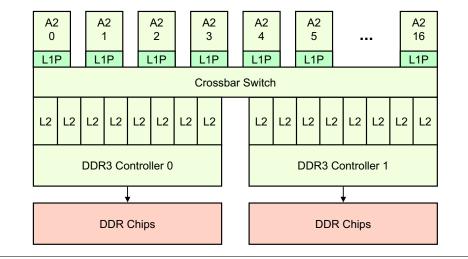

| 4.1 Memory system overview       26         4.1.1 L1 prefetch cache overview       26         4.1.2 L2 cache functional overview       28         4.1.3 Boot eDRAM overview       28         4.1.3 Boot eDRAM overview       28         4.1.3 Boot eDRAM overview       28         4.1.4 Boot eDRAM overview       28         4.1.5 Memory management       29         4.4 Shared memory       29         4.5 Persistent memory       29         4.5 Presistent memory       29         4.5 Compute node randisk       30         4.6 Compute node randisk       30         4.7 Support for the /prof file system       31         4.8 L1P prefetcher       32         4.8.1 Linear stream prefetcher overview       34         4.8.2 Perfect prefetcher overview       34         4.8.3 L1P prefetcher API descriptions       38         4.8.4 Performance considerations       52         4.9 L2 atomic operations       53         4.10 Speculative execution       53         4.11 Support for dynamic linking       54         4.12 Transactional memory       54         5.1 Lightweight principles       56         5.2 Kernel access       56         5.2.1 Application prog                                                                       | Chapter 4. Memory                                                                                                                                                                        | 25                               |

| 4.1.2       L2 cache functional overview       28         4.1.3       Boot eDPAM overview       28         4.2       Memory management       29         4.3       Memory protection       29         4.4       Shared memory       29         4.5       Persistent memory       30         4.6       Compute node ramdisk       30         4.7       Support for the /proc file system       31         4.8       L1P prefetcher.       32         4.8.1       Linear stream prefetcher overview       33         4.8.2       Perfect prefetcher overview       34         4.8.3       L1P prefetcher API descriptions       38         4.8.4       Performance considerations       52         4.9       L2 atomic operations.       53         4.10       Speculative execution       53         4.11       Support for dynamic linking.       54         4.12       Transactional memory       54         4.12       Transactional memory       54         5.2       Kernel access       56         5.2.1       Application programming interfaces       56         5.2.2       System calls       63         6.1 <td< td=""><td></td><td></td></td<>                                                                                                   |                                                                                                                                                                                          |                                  |

| 4.1.2       L2 cache functional overview       28         4.1.3       Boot eDPAM overview       28         4.2       Memory management       29         4.3       Memory protection       29         4.4       Shared memory       29         4.5       Persistent memory       30         4.6       Compute node ramdisk       30         4.7       Support for the /proc file system       31         4.8       L1P prefetcher.       32         4.8.1       Linear stream prefetcher overview       33         4.8.2       Perfect prefetcher overview       34         4.8.3       L1P prefetcher API descriptions       38         4.8.4       Performance considerations       52         4.9       L2 atomic operations.       53         4.10       Speculative execution       53         4.11       Support for dynamic linking.       54         4.12       Transactional memory       54         4.12       Transactional memory       54         5.2       Kernel access       56         5.2.1       Application programming interfaces       56         5.2.2       System calls       63         6.1 <td< td=""><td>4.1.1 L1 prefetch cache overview</td><td>26</td></td<>                                                                 | 4.1.1 L1 prefetch cache overview                                                                                                                                                         | 26                               |

| 4.2 Memory management       29         4.3 Memory protection       29         4.4 Shared memory.       29         4.5 Persistent memory       30         4.6 Compute node ramdisk.       30         4.7 Support for the /proc file system       31         4.8 L1P prefetcher.       32         4.8.1 Linear stream prefetcher overview       33         4.8.2 Perfect prefetcher overview       34         4.8.3 L1P prefetcher API descriptions       38         4.8.4 Performance considerations       52         4.9 L2 atomic operations.       53         4.10 Speculative execution       53         4.11 Support for dynamic linking.       54         4.12 Transactional memory.       54         Chapter 5. Compute Node Kernel interfaces       55         5.1 Lightweight principles       56         5.2.2 System programming interfaces       56         5.2.2 System programming interfaces       56         5.2.3 System calls       63         Chapter 6. Parallel paradigms       65         6.2.3 Not waiting for the MPI_Test function       67         6.2.4 Flooding the network with messages       70         6.2.5 Deadlocking the system       70         6.2.6 Violating MPI buffer ownershi                                    |                                                                                                                                                                                          |                                  |

| 4.3 Memory protection       29         4.4 Shared memory.       29         4.5 Persistent memory       30         4.6 Compute node ramdisk.       30         4.7 Support for the /proc file system       31         4.8 L1P prefetcher       32         4.8.1 Linear stream prefetcher overview       33         4.8.2 Perfect prefetcher overview       34         4.8.3 L1P prefetcher API descriptions       38         4.8.4 Performance considerations       52         4.9 L2 atomic operations       53         4.10 Speculative execution       53         4.11 Support for dynamic linking       54         4.12 Transactional memory.       54         Chapter 5. Compute Node Kernel interfaces       55         5.1 Lightweight principles       56         5.2.1 Application programming interfaces       56         5.2.2 System programming interfaces       56         5.2.1 Application programming interfaces       56         6.2 Blue Gene/Q MPI implementation       67         6.2.1 High-performance network for efficient parallel execution       67         6.2.2 Forcing MPI to allocate too much memory.       69         6.2.3 Not waiting for the MPI_Test function       70         6.2.4 Flooding the network with message | 4.1.3 Boot eDRAM overview                                                                                                                                                                | 28                               |

| 4.3 Memory protection       29         4.4 Shared memory.       29         4.5 Persistent memory       30         4.6 Compute node ramdisk.       30         4.7 Support for the /proc file system       31         4.8 L1P prefetcher       32         4.8.1 Linear stream prefetcher overview       33         4.8.2 Perfect prefetcher overview       34         4.8.3 L1P prefetcher API descriptions       38         4.8.4 Performance considerations       52         4.9 L2 atomic operations       53         4.10 Speculative execution       53         4.11 Support for dynamic linking       54         4.12 Transactional memory.       54         Chapter 5. Compute Node Kernel interfaces       55         5.1 Lightweight principles       56         5.2.1 Application programming interfaces       56         5.2.2 System programming interfaces       56         5.2.1 Application programming interfaces       56         6.2 Blue Gene/Q MPI implementation       67         6.2.1 High-performance network for efficient parallel execution       67         6.2.2 Forcing MPI to allocate too much memory.       69         6.2.3 Not waiting for the MPI_Test function       70         6.2.4 Flooding the network with message | 4.2 Memory management                                                                                                                                                                    | 29                               |

| 4.4       Shared memory.       29         4.5       Persistent memory.       30         4.6       Compute node ramdisk.       30         4.7       Support for the /proc file system.       31         4.8       L1P prefetcher.       32         4.8.1       Linear stream prefetcher overview       33         4.8.2       Perfect prefetcher overview       34         4.8.3       L1P prefetcher API descriptions       38         4.8.4       Performance considerations       52         4.9       L2 atomic operations       53         4.10       Speculative execution       53         4.11       Support for dynamic linking       54         4.12       Transactional memory.       54         Chapter 5.       Compute Node Kernel interfaces       55         5.1       Lightweight principles       56         5.2       Kernel access       56         5.2.2       System programming interface       62         5.3       System calls       63         Chapter 6.       Parallel paradigms       65         6.1       Programming model       66         6.2       Forcing MPI to allocate too much memory       69                                                                                                                      |                                                                                                                                                                                          |                                  |

| 4.6 Compute node ramdisk       30         4.7 Support for the /proc file system       31         4.8 L1P prefetcher       32         4.8.1 Linear stream prefetcher overview       33         4.8.2 Perfect prefetcher overview       34         4.8.3 L1P prefetcher API descriptions       38         4.8.4 Performance considerations       52         4.9 L2 atomic operations       53         4.10 Speculative execution       53         4.11 Support for dynamic linking       54         4.12 Transactional memory       54         Chapter 5. Compute Node Kernel interfaces       55         5.1 Lightweight principles       56         5.2 Kernel access       56         5.2.1 Application programming interfaces       56         5.2.2 System programming interfaces       56         5.3 System calls       63         Chapter 6. Parallel paradigms       65         6.1 Programming model       66         6.2 Blue Gene/Q MPI implementation.       67         6.2.3 Not waiting for the MPI_Test function       70         6.2.4 Flooding the network with messages       70         6.2.5 Deadlocking the system       70         6.2.6 Violating MPI buffer ownership rules.       71         6.                                    |                                                                                                                                                                                          |                                  |

| 4.7 Support for the /proc file system       31         4.8 L1P prefetcher.       32         4.8.1 Linear stream prefetcher overview       33         4.8.2 Perfect prefetcher overview       34         4.8.3 L1P prefetcher API descriptions       38         4.8.4 Performance considerations       52         4.9 L2 atomic operations       53         4.10 Speculative execution       53         4.11 Support for dynamic linking       54         4.12 Transactional memory       54         4.12 Transactional memory       54         Chapter 5. Compute Node Kernel interfaces       55         5.1 Lightweight principles       56         5.2.2 System programming interfaces       56         5.2.3 System calls       63         Chapter 6. Parallel paradigms       65         6.1 Programming model       66         6.2 Blue Gene/Q MPI implementation       67         6.2.4 Flooding the MPI_Test function       70         6.2.5 Deadlocking the system       70         6.2.6 Violating MPI buffer ownership rules       71         6.2.7 Buffer alignment sensitivity       71         6.3.8 Due Gene/Q MPI extensions       72         6.3.1 Changing class-route usage at run time       72                                        | 4.5 Persistent memory                                                                                                                                                                    | 30                               |

| 4.8 L1P prefetcher.       32         4.8.1 Linear stream prefetcher overview       33         4.8.2 Perfect prefetcher overview       34         4.8.3 L1P prefetcher API descriptions       38         4.8.4 Performance considerations       52         4.9 L2 atomic operations       53         4.10 Speculative execution       53         4.11 Support for dynamic linking       54         4.12 Transactional memory       54         4.12 Transactional memory       54         Chapter 5. Compute Node Kernel interfaces       55         5.1 Lightweight principles       56         5.2 Kernel access       56         5.2.1 Application programming interfaces       56         5.2.2 System programming interface       62         5.3 System calls       63         Chapter 6. Parallel paradigms       65         6.1 Programming model       66         6.2 Blue Gene/Q MPI implementation       67         6.2.2 Forcing MPI to allocate too much memory       69         6.2.3 Not waiting for the MPI_Test function       70         6.2.4 Hooding the network with messages       70         6.2.5 Deadlocking the system       70         6.2.6 Violating MPI buffer ownership rules       71                                         | 4.6 Compute node ramdisk                                                                                                                                                                 | 30                               |

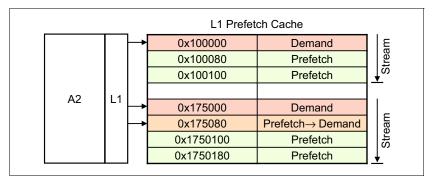

| 4.8.1 Linear stream prefetcher overview       33         4.8.2 Perfect prefetcher overview       34         4.8.3 L1P prefetcher API descriptions       38         4.8.4 Performance considerations       52         4.9 L2 atomic operations       53         4.10 Speculative execution       53         4.11 Support for dynamic linking       54         4.12 Transactional memory       54         Chapter 5. Compute Node Kernel interfaces       55         5.1 Lightweight principles       56         5.2 Kernel access       56         5.2.1 Application programming interfaces       56         5.2.2 System programming interface       62         5.3 System calls       63         Chapter 6. Parallel paradigms       65         6.1 Programming model       66         6.2 Blue Gene/Q MPI implementation.       67         6.2.1 High-performance network for efficient parallel execution       67         6.2.2 Forcing MPI to allocate too much memory       69         6.2.3 Not waiting for the MPI_Test function.       70         6.2.4 Flooding the network with messages       70         6.2.5 Deadlocking the system       70         6.2.6 Violating MPI buffer ownership rules.       71         6.3 Uchanging class-route  | 4.7 Support for the /proc file system                                                                                                                                                    | 31                               |

| 4.8.2 Perfect prefetcher overview       34         4.8.3 L1P prefetcher API descriptions       38         4.8.4 Performance considerations       52         4.9 L2 atomic operations       53         4.10 Speculative execution       53         4.11 Support for dynamic linking       54         4.12 Transactional memory       54         Chapter 5. Compute Node Kernel interfaces       55         5.1 Lightweight principles       56         5.2 Kernel access       56         5.2.1 Application programming interfaces       56         5.2.2 System programming interface       62         5.3 System calls       63         Chapter 6. Parallel paradigms       65         6.1 Programming model       66         6.2 Blue Gene/Q MPI implementation.       67         6.2.1 High-performance network for efficient parallel execution       67         6.2.3 Not waiting for the MPI_Test function       70         6.2.4 Flooding the network with messages       70         6.2.5 Deadlocking the system       70         6.2.6 Violating MPI buffer ownership rules       71         6.3 Blue Gene/Q MPI extensions       72         6.3.1 Changing class-route usage at run time       72         6.3.2 Determining hardware properties< | 4.8 L1P prefetcher                                                                                                                                                                       | 32                               |

| 4.8.3 L1P prefetcher API descriptions       38         4.8.4 Performance considerations       52         4.9 L2 atomic operations.       53         4.10 Speculative execution       53         4.11 Support for dynamic linking.       54         4.12 Transactional memory.       54         Chapter 5. Compute Node Kernel interfaces       55         5.1 Lightweight principles       56         5.2 Kernel access       56         5.2.1 Application programming interfaces       56         5.2.2 System programming interfaces       63         Chapter 6. Parallel paradigms       65         6.1 Programming model       66         6.2 Blue Gene/Q MPI implementation       67         6.2.1 High-performance network for efficient parallel execution       67         6.2.2 Forcing MPI to allocate too much memory       69         6.2.3 Not waiting for the MPI_Test function       70         6.2.4 Flooding the network with messages       70         6.2.5 Deadlocking the system       70         6.2.6 Violating MPI buffer ownership rules       71         6.3 Blue Gene/Q MPI extensions       72         6.3.1 Changing class-route usage at run time       72         6.3.2 Determining hardware properties       73            | 4.8.1 Linear stream prefetcher overview                                                                                                                                                  | 33                               |

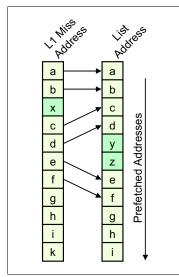

| 4.8.4 Performance considerations       52         4.9 L2 atomic operations       53         4.10 Speculative execution       53         4.11 Support for dynamic linking       54         4.12 Transactional memory       54         Chapter 5. Compute Node Kernel interfaces       55         5.1 Lightweight principles       56         5.2 Kernel access       56         5.2.1 Application programming interfaces       56         5.2.2 System programming interface       62         5.3 System calls       63         Chapter 6. Parallel paradigms       65         6.1 Programming model       66         6.2 Blue Gene/Q MPI implementation       67         6.2.1 High-performance network for efficient parallel execution       67         6.2.2 Forcing MPI to allocate too much memory       69         6.2.3 Not waiting for the MPI_Test function       70         6.2.4 Flooding the network with messages       70         6.2.5 Deadlocking the system       70         6.2.6 Violating MPI buffer ownership rules       71         6.3 Blue Gene/Q MPI extensions       72         6.3.1 Changing class-route usage at run time       72         6.3.2 Determining hardware properties       73                                     | 4.8.2 Perfect prefetcher overview                                                                                                                                                        | 34                               |

| 4.9 L2 atomic operations.       53         4.10 Speculative execution       53         4.11 Support for dynamic linking.       54         4.12 Transactional memory.       54         Chapter 5. Compute Node Kernel interfaces       55         5.1 Lightweight principles       56         5.2 Kernel access       56         5.2.1 Application programming interfaces       56         5.2.2 System programming interfaces       56         5.2.3 System calls       63         Chapter 6. Parallel paradigms       65         6.1 Programming model       66         6.2 Blue Gene/Q MPI implementation       67         6.2.1 High-performance network for efficient parallel execution       67         6.2.2 Forcing MPI to allocate too much memory       69         6.2.3 Not waiting for the MPI_Test function       70         6.2.4 Flooding the network with messages       70         6.2.5 Deadlocking the system       70         6.2.6 Violating MPI buffer ownership rules       71         6.3.1 Changing class-route usage at run time       72         6.3.2 Determining hardware properties       73         6.4 MPI functions       73                                                                                              |                                                                                                                                                                                          |                                  |

| 4.10       Speculative execution       53         4.11       Support for dynamic linking       54         4.12       Transactional memory       54         Chapter 5.       Compute Node Kernel interfaces       55         5.1       Lightweight principles       56         5.2       Kernel access       56         5.2.1       Application programming interfaces       56         5.2.2       System programming interface       62         5.3       System calls       63         Chapter 6.       Parallel paradigms       65         6.1       Programming model       66         6.2       Blue Gene/Q MPI implementation       67         6.2.1       High-performance network for efficient parallel execution       67         6.2.3       Not waiting for the MPI_Test function       70         6.2.4       Flooding the network with messages       70         6.2.5       Deadlocking the system       70         6.2.6       Violating MPI buffer ownership rules       71         6.3       Blue Gene/Q MPI extensions       72         6.3.1       Changing class-route usage at run time       72         6.3.1       Changing class-route usage at run time       72                                                                 |                                                                                                                                                                                          |                                  |

| 4.11       Support for dynamic linking.       54         4.12       Transactional memory.       54         Chapter 5.       Compute Node Kernel interfaces       55         5.1       Lightweight principles       56         5.2       Kernel access       56         5.2.1       Application programming interfaces       56         5.2.2       System programming interface       62         5.3       System calls       63         Chapter 6.       Parallel paradigms       65         6.1       Programming model       66         6.2       Blue Gene/Q MPI implementation       67         6.2.1       High-performance network for efficient parallel execution       67         6.2.3       Not waiting for the MPI_Test function       70         6.2.4       Flooding the network with messages       70         6.2.5       Deadlocking the system       70         6.2.6       Violating MPI buffer ownership rules       71         6.3       Blue Gene/Q MPI extensions       72         6.3.1       Changing class-route usage at run time       72         6.3.1       Changing class-route usage at run time       73         6.4       MPI functions       73 <td>4.9 L2 atomic operations</td> <td>53</td>                          | 4.9 L2 atomic operations                                                                                                                                                                 | 53                               |

| 4.12 Transactional memory.       54         Chapter 5. Compute Node Kernel interfaces       55         5.1 Lightweight principles       56         5.2 Kernel access       56         5.2.1 Application programming interfaces       56         5.2.2 System programming interface       62         5.3 System calls       63         Chapter 6. Parallel paradigms       65         6.1 Programming model       66         6.2 Blue Gene/Q MPI implementation       67         6.2.1 High-performance network for efficient parallel execution       67         6.2.2 Forcing MPI to allocate too much memory       69         6.2.3 Not waiting for the MPI_Test function       70         6.2.4 Flooding the network with messages       70         6.2.5 Deadlocking the system       70         6.2.6 Violating MPI buffer ownership rules       71         6.3 Blue Gene/Q MPI extensions       72         6.3.1 Changing class-route usage at run time       72         6.3.2 Determining hardware properties       73                                                                                                                                                                                                                              | 4.10 Speculative execution                                                                                                                                                               | 53                               |

| Chapter 5. Compute Node Kernel interfaces       55         5.1 Lightweight principles       56         5.2 Kernel access       56         5.2.1 Application programming interfaces       56         5.2.2 System programming interface       62         5.3 System calls       63         Chapter 6. Parallel paradigms       65         6.1 Programming model       66         6.2 Blue Gene/Q MPI implementation       67         6.2.1 High-performance network for efficient parallel execution       67         6.2.2 Forcing MPI to allocate too much memory       69         6.2.3 Not waiting for the MPI_Test function       70         6.2.4 Flooding the network with messages       70         6.2.5 Deadlocking the system       70         6.2.6 Violating MPI buffer ownership rules       71         6.3 Blue Gene/Q MPI extensions       72         6.3.1 Changing class-route usage at run time       72         6.3.2 Determining hardware properties       73                                                                                                                                                                                                                                                                          | 4.11 Support for dynamic linking                                                                                                                                                         | 54                               |

| 5.1 Lightweight principles       56         5.2 Kernel access       56         5.2.1 Application programming interfaces       56         5.2.2 System programming interface       62         5.3 System calls       63         Chapter 6. Parallel paradigms         6.1 Programming model       66         6.2 Blue Gene/Q MPI implementation       67         6.2.1 High-performance network for efficient parallel execution       67         6.2.2 Forcing MPI to allocate too much memory       69         6.2.3 Not waiting for the MPI_Test function       70         6.2.4 Flooding the network with messages       70         6.2.5 Deadlocking the system       70         6.2.6 Violating MPI buffer ownership rules       71         6.3 Blue Gene/Q MPI extensions       72         6.3.1 Changing class-route usage at run time       72         6.3.2 Determining hardware properties       73                                                                                                                                                                                                                                                                                                                                              | 4.12 Transactional memory.                                                                                                                                                               | 54                               |

| 5.1 Lightweight principles       56         5.2 Kernel access       56         5.2.1 Application programming interfaces       56         5.2.2 System programming interface       62         5.3 System calls       63         Chapter 6. Parallel paradigms         6.1 Programming model       66         6.2 Blue Gene/Q MPI implementation       67         6.2.1 High-performance network for efficient parallel execution       67         6.2.2 Forcing MPI to allocate too much memory       69         6.2.3 Not waiting for the MPI_Test function       70         6.2.4 Flooding the network with messages       70         6.2.5 Deadlocking the system       70         6.2.6 Violating MPI buffer ownership rules       71         6.3 Blue Gene/Q MPI extensions       72         6.3.1 Changing class-route usage at run time       72         6.3.2 Determining hardware properties       73                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                          |                                  |

| 5.2 Kernel access       56         5.2.1 Application programming interfaces       56         5.2.2 System programming interface       62         5.3 System calls       63         Chapter 6. Parallel paradigms         6.1 Programming model       65         6.2 Blue Gene/Q MPI implementation       67         6.2.1 High-performance network for efficient parallel execution       67         6.2.2 Forcing MPI to allocate too much memory       69         6.2.3 Not waiting for the MPI_Test function       70         6.2.4 Flooding the network with messages       70         6.2.5 Deadlocking the system       70         6.2.6 Violating MPI buffer ownership rules       71         6.3 Blue Gene/Q MPI extensions       72         6.3.1 Changing class-route usage at run time       72         6.3.2 Determining hardware properties       73                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                          |                                  |

| 5.2.1 Application programming interfaces565.2.2 System programming interface625.3 System calls63Chapter 6. Parallel paradigms656.1 Programming model666.2 Blue Gene/Q MPI implementation676.2.1 High-performance network for efficient parallel execution676.2.2 Forcing MPI to allocate too much memory696.2.3 Not waiting for the MPI_Test function706.2.4 Flooding the network with messages706.2.5 Deadlocking the system706.2.6 Violating MPI buffer ownership rules716.3 Blue Gene/Q MPI extensions726.3.1 Changing class-route usage at run time726.3.2 Determining hardware properties736.4 MPI functions73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                          |                                  |

| 5.2.2 System programming interface       62         5.3 System calls       63         Chapter 6. Parallel paradigms       65         6.1 Programming model       66         6.2 Blue Gene/Q MPI implementation       67         6.2.1 High-performance network for efficient parallel execution       67         6.2.2 Forcing MPI to allocate too much memory       69         6.2.3 Not waiting for the MPI_Test function       70         6.2.4 Flooding the network with messages       70         6.2.5 Deadlocking the system       70         6.2.6 Violating MPI buffer ownership rules.       71         6.3 Blue Gene/Q MPI extensions       72         6.3.1 Changing class-route usage at run time       72         6.3.2 Determining hardware properties       73         6.4 MPI functions       73                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                          |                                  |

| 5.3 System calls63Chapter 6. Parallel paradigms656.1 Programming model666.2 Blue Gene/Q MPI implementation676.2.1 High-performance network for efficient parallel execution676.2.2 Forcing MPI to allocate too much memory696.2.3 Not waiting for the MPI_Test function706.2.4 Flooding the network with messages706.2.5 Deadlocking the system706.2.6 Violating MPI buffer ownership rules716.3 Blue Gene/Q MPI extensions726.3.1 Changing class-route usage at run time726.3.2 Determining hardware properties736.4 MPI functions73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                          |                                  |

| Chapter 6. Parallel paradigms656.1 Programming model666.2 Blue Gene/Q MPI implementation676.2.1 High-performance network for efficient parallel execution676.2.2 Forcing MPI to allocate too much memory696.2.3 Not waiting for the MPI_Test function706.2.4 Flooding the network with messages706.2.5 Deadlocking the system706.2.6 Violating MPI buffer ownership rules716.2.7 Buffer alignment sensitivity716.3 Blue Gene/Q MPI extensions726.3.1 Changing class-route usage at run time726.3.2 Determining hardware properties736.4 MPI functions73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                          |                                  |

| 6.1 Programming model666.2 Blue Gene/Q MPI implementation.676.2.1 High-performance network for efficient parallel execution676.2.2 Forcing MPI to allocate too much memory696.2.3 Not waiting for the MPI_Test function706.2.4 Flooding the network with messages706.2.5 Deadlocking the system706.2.6 Violating MPI buffer ownership rules716.2.7 Buffer alignment sensitivity716.3 Blue Gene/Q MPI extensions726.3.1 Changing class-route usage at run time726.3.2 Determining hardware properties736.4 MPI functions73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                          | 03                               |

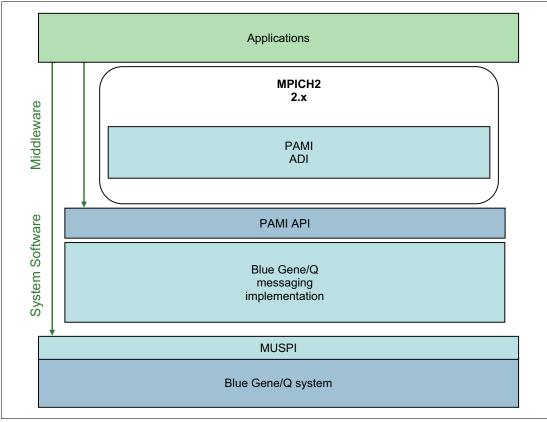

| 6.1 Programming model666.2 Blue Gene/Q MPI implementation.676.2.1 High-performance network for efficient parallel execution676.2.2 Forcing MPI to allocate too much memory696.2.3 Not waiting for the MPI_Test function706.2.4 Flooding the network with messages706.2.5 Deadlocking the system706.2.6 Violating MPI buffer ownership rules716.2.7 Buffer alignment sensitivity716.3 Blue Gene/Q MPI extensions726.3.1 Changing class-route usage at run time726.3.2 Determining hardware properties736.4 MPI functions73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Chapter 6. Parallel paradigms                                                                                                                                                            | 65                               |

| 6.2 Blue Gene/Q MPI implementation.676.2.1 High-performance network for efficient parallel execution676.2.2 Forcing MPI to allocate too much memory696.2.3 Not waiting for the MPI_Test function706.2.4 Flooding the network with messages706.2.5 Deadlocking the system706.2.6 Violating MPI buffer ownership rules716.2.7 Buffer alignment sensitivity716.3 Blue Gene/Q MPI extensions726.3.1 Changing class-route usage at run time736.4 MPI functions73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                          |                                  |

| 6.2.1 High-performance network for efficient parallel execution676.2.2 Forcing MPI to allocate too much memory696.2.3 Not waiting for the MPI_Test function706.2.4 Flooding the network with messages706.2.5 Deadlocking the system706.2.6 Violating MPI buffer ownership rules716.2.7 Buffer alignment sensitivity716.3 Blue Gene/Q MPI extensions726.3.1 Changing class-route usage at run time736.4 MPI functions73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                          |                                  |

| 6.2.2 Forcing MPI to allocate too much memory696.2.3 Not waiting for the MPI_Test function706.2.4 Flooding the network with messages706.2.5 Deadlocking the system706.2.6 Violating MPI buffer ownership rules716.2.7 Buffer alignment sensitivity716.3 Blue Gene/Q MPI extensions726.3.1 Changing class-route usage at run time726.3.2 Determining hardware properties736.4 MPI functions73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •                                                                                                                                                                                        |                                  |

| 6.2.3 Not waiting for the MPI_Test function706.2.4 Flooding the network with messages706.2.5 Deadlocking the system706.2.6 Violating MPI buffer ownership rules716.2.7 Buffer alignment sensitivity716.3 Blue Gene/Q MPI extensions726.3.1 Changing class-route usage at run time726.3.2 Determining hardware properties736.4 MPI functions73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                          |                                  |

| 6.2.4 Flooding the network with messages706.2.5 Deadlocking the system706.2.6 Violating MPI buffer ownership rules716.2.7 Buffer alignment sensitivity716.3 Blue Gene/Q MPI extensions726.3.1 Changing class-route usage at run time726.3.2 Determining hardware properties736.4 MPI functions73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                          |                                  |

| 6.2.5 Deadlocking the system706.2.6 Violating MPI buffer ownership rules.716.2.7 Buffer alignment sensitivity716.3 Blue Gene/Q MPI extensions726.3.1 Changing class-route usage at run time726.3.2 Determining hardware properties736.4 MPI functions73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •                                                                                                                                                                                        |                                  |

| 6.2.6 Violating MPI buffer ownership rules.716.2.7 Buffer alignment sensitivity.716.3 Blue Gene/Q MPI extensions726.3.1 Changing class-route usage at run time.726.3.2 Determining hardware properties736.4 MPI functions73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.2.4 Flooding the network with messages                                                                                                                                                 | 10                               |

| 6.2.7 Buffer alignment sensitivity716.3 Blue Gene/Q MPI extensions726.3.1 Changing class-route usage at run time726.3.2 Determining hardware properties736.4 MPI functions73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | · · ·                                                                                                                                                                                    |                                  |

| 6.3 Blue Gene/Q MPI extensions       72         6.3.1 Changing class-route usage at run time       72         6.3.2 Determining hardware properties       73         6.4 MPI functions       73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6.2.5 Deadlocking the system                                                                                                                                                             | 70                               |

| 6.3.1 Changing class-route usage at run time726.3.2 Determining hardware properties736.4 MPI functions73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6.2.5 Deadlocking the system         6.2.6 Violating MPI buffer ownership rules                                                                                                          | 70<br>71                         |

| 6.3.2 Determining hardware properties736.4 MPI functions73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6.2.5 Deadlocking the system         6.2.6 Violating MPI buffer ownership rules.         6.2.7 Buffer alignment sensitivity                                                              | 70<br>71<br>71                   |

| 6.4 MPI functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>6.2.5 Deadlocking the system</li> <li>6.2.6 Violating MPI buffer ownership rules</li> <li>6.2.7 Buffer alignment sensitivity</li> <li>6.3 Blue Gene/Q MPI extensions</li> </ul> | 70<br>71<br>71<br>72             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <ul> <li>6.2.5 Deadlocking the system</li></ul>                                                                                                                                          | 70<br>71<br>71<br>72<br>72       |